# DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING LAB MANUAL Analog Circuits Lab II - B. Tech. II - Semester

PRASAD V POTLURI SIDDHARTHA INSTITUTE OF TECHNOLOGY (Autonomous, Accredited by NBA & NAAC, an ISO 9001:2008 certified institution) (Sponsored by Siddhartha Academy of General & Technical Education) VIJAYAWADA – 520 007, ANDHRA PRADESH

# PRASAD V POTLURI SIDDHARTHA INSTITUTE OF TECHNOLOGY DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING ANALOG CIRCUITS LAB

| Course Code                          | 20EC3451     | Year                       | II    | Semester      | II   |

|--------------------------------------|--------------|----------------------------|-------|---------------|------|

| Course<br>Category                   | Program Core | Branch                     | ECE   | Course Type   | Lab  |

| Credits                              | 1.5          | L-T-P                      | 0-0-3 | Prerequisites | EDAC |

| Continuous<br>Internal<br>Evaluation | 15           | Semester End<br>Evaluation | 35    | Total Marks   | 50   |

| Course | Outcomes SID HARTHAINS 77                                       |

|--------|-----------------------------------------------------------------|

| Upon s | uccessful completion of the course, the student will be able to |

| CO1    | Analyze the feedback amplifiers using FET (L4)                  |

| CO2    | Evaluate the performance of Power Amplifiers using BJT(L5)      |

| CO3    | <b>Design</b> the various applications using Op-amp (L6)        |

| CO4    | <b>Design</b> the various applications using IC 555 Timer (L6)  |

| CO5    | Make an effective report based on experiments.                  |

I.

PR/

DGY

| Mapping                                        | Mapping of course outcomes with Program outcomes (CO/ PO/PSO Matrix) |       |        |         |         |       |       |        |       |        |        |       |      |      |

|------------------------------------------------|----------------------------------------------------------------------|-------|--------|---------|---------|-------|-------|--------|-------|--------|--------|-------|------|------|

| Note: 1                                        | Note: 1- Weak correlation 2-Medium correlation 3-Strong correlation  |       |        |         |         |       |       |        |       |        |        |       |      |      |

|                                                | * - A                                                                | verag | e valu | e indio | cates c | ourse | corre | latior | strei | ngth w | ith ma | apped | PO   |      |

| COs                                            | PO1                                                                  | PO2   | PO3    | PO4     | PO5     | PO6   | PO7   | PO8    | PO9   | PO10   | PO11   | PO12  | PSO1 | PSO2 |

| CO1                                            |                                                                      | 1     |        |         | 3       |       |       |        | 3     |        |        |       | 3    |      |

| CO2                                            |                                                                      |       |        | 2       | 3       |       |       |        | 3     |        |        |       | 3    |      |

| CO3                                            |                                                                      |       | 3      |         | 3       |       |       |        | 3     |        |        |       | 3    |      |

| CO4                                            |                                                                      |       | 2      |         | 3       |       |       |        | 3     |        |        |       | 3    |      |

| CO5                                            |                                                                      |       |        |         |         |       |       |        |       | 3      |        |       |      |      |

| Average*<br>(Rounded to<br>nearest<br>integer) |                                                                      | 1     | 3      | 2       | 3       |       |       |        | 3     | 3      |        |       | 3    |      |

# LIST OF EXPERIMENTS

|              | Syllabus                                                                                                             |              |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------|--------------|--|--|--|--|

| Expt.<br>No. | Contents                                                                                                             | Mapped<br>CO |  |  |  |  |

| Ι            | Calculation of gain, input resistance, output resistance of a feedback amplifier with and without feedback using FET | CO1,CO5      |  |  |  |  |

| II           | Design and verify an RC phase-shift oscillator for a given frequency using Op-Amp                                    | CO3,CO5      |  |  |  |  |

| III          | Design and verify a Wein-bridge Oscillator for a given frequency using Op-Amp                                        | CO3,CO5      |  |  |  |  |

| IV           | Design and verify a Colpitt's Oscillator for a given frequency<br>using Op- Amp                                      | CO3,CO5      |  |  |  |  |

| V            | Evaluate the Conversion efficiency of a Class A power amplifier using BJT                                            | CO2,CO5      |  |  |  |  |

| VI           | Evaluate the Conversion efficiency of Class B Push - pull power<br>amplifier using BJT                               | CO2,CO5      |  |  |  |  |

| VII          | Design and Simulate the RC differentiator using Op-Amp                                                               | CO3,CO5      |  |  |  |  |

| VIII         | Design and Simulate the RC integrator using Op-Amp                                                                   | CO3,CO5      |  |  |  |  |

| IX           | Design and verify Adder and Subtractor circuits using<br>Operational Amplifier                                       | CO3,CO5      |  |  |  |  |

| Х            | Design and verify an Astable multivibrator using 555 timer                                                           | CO4,CO5      |  |  |  |  |

| XI           | Design and verify Monstable multivibrator using 741Op-Amp                                                            | CO3,CO5      |  |  |  |  |

| XII          | Design and verify Monstable multivibrator using 555 timer                                                            | CO4,CO5      |  |  |  |  |

| XIII         | Design and verify an Astable multivibrator using 741 Op-Amp                                                          | CO3,CO5      |  |  |  |  |

| XIV          | Design and verify LPF and HPF using Op-Amp                                                                           | CO3,CO5      |  |  |  |  |

| XV           | Design and verify a 4 bit DAC using OP-Amp                                                                           | CO3,CO5      |  |  |  |  |

#### **Learning Resources**

#### **Text Books**

1. Adel S. Sedra, Kenneth C. Smith, Arun N. Chandorkar, Microelectronic Circuits, 6/e,Oxford

University Press, 2013.

2. D Choudhury Roy, Shail B. Jain, Linear Integrated Circuits, New Age International, 2003

3. Ramakanth Gayakward, Op-Amps and Linear Integrated Circuits, 4/e, Pearson Education,2007

#### **Reference Books**

- 1. Behzad Razavi, Fundamentals of Microelectronics, 2/e, Wiley Student Edition, 2013.

- 2. R.F Coughlin, F.F Driscoll, Op-Amps and Linear Integrated Circuits, 6/e, Pearson, 2008.

- 3. Sergio Franco, Design with Operational Amplifiers and Analog Integrated Circuits, 3/e,Tata Mc-Graw Hill, 2002.

#### **INSTRUCTIONS TO THE STUDENTS**

1. Students are required to attend all labs.

2. Students have to bring the lab manual cum observation book, record etc. along with them whenever they come for lab work.

3. Should learn the prelab questions. Read through the lab experiment to familiarize themselves with the components and assembly sequence.

4. Should utilize 3 hours' time properly to perform the experiment and to record the readings. Do the calculations, and take signature from the instructor.

5. If the experiment is not completed in the stipulated time, the pending work has to be carried out in the leisure hours or extended hours.

6. Should submit the completed record book according to the deadlines set up by the instructor.

7. For practical subjects there shall be a continuous evaluation during the semester for 15 internal marks and 35 end examination marks.

8. Out of 15 internal marks, 10 marks shall be awarded for day-to-day work and 5 marks to be awarded by conducting an internal laboratory test.

# FET AMPLIFIER WITH AND WITHOUT FEEDBACK

# AIM:

To obtain gain, input resistance, output resistance of a feedback amplifier with and without feedback using FET.

DHARTHA INS 7

**Experimental Requirements:**

MOSFET -2N7000

Resistors

Capacitors

Regulated Power Supply

CRO

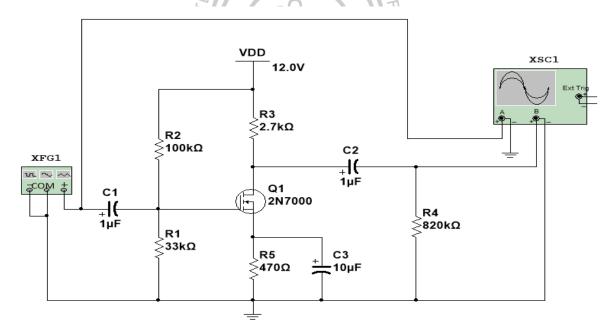

#### **Circuit Diagram:**

#### **Design:**

Assume  $V_{DD}=12V$ ,  $V_{RD}=5v$ ,  $V_{DS}=6V$ ,  $I_D=2Mamp$

$$R_D = \frac{V_{RD}}{I_D} = \frac{5}{2 \times 10 \times 10^{-3}} = 2.5 k\Omega, \text{ Use } 2.7 \text{k}\Omega \text{ resistor}$$

Now the voltage across the source side resistance  $V_{RS} = V_{DD} - V_{DS} - V_{RD} = 12-6-5=1V$

As,  $I_S = I_D$  (No current flows through the gate)

$$R_S = \frac{V_{RS}}{I_D} = \frac{1}{2 \times 10 \times 10^{-3}} = 500\Omega$$

, Use 470 $\Omega$  resistor

#### Voltage- divider bias circuit design:

Assume  $R_1=100k\Omega$ . By, Voltage Division rule,  $R_2$  can be obtained as,

$$V_G = V_{DD} \times \frac{R_2}{R_1 + R_2}$$

Selecting the value of  $V_G$  as 4V

$$4 = 12 \times \frac{R_2}{100 \times 10 \times 10^3 + R_2} \\ R_2 \sim 47 k\Omega$$

# **Design of capacitors:** Assume impedance of coupling capacitor be $H_{C1} \ll 1.5k\Omega$ Therefore, $\frac{1}{2\pi f C_1} \leq 1.5k\Omega$ i.e., $\frac{1}{2\pi f C_1 2\pi f C_1} \leq 1.5k\Omega$ Given, the frequency of the input signal is 100Hz. $C_1=1.06\mu f$ . Let $C_1=C_2=1\mu f$ For the bypass capacitor, $X_{cs} = \frac{1}{2\pi f C_s} \leq 150\Omega$ $C_s= 10\mu f$

#### **Procedure:**

1. Set up the circuit as shown in the figure.

2. Apply an input signal of 0.2V (peak-to-peak) at 1000 Hz.

3. Observe the output on the CRO.

4. Vary the frequency of the input signal over a range of values (from 50Hz to a few MHz).

5.Obtain the frequency response which is a graph between frequency (x- axis) and gain in dB (y-axis).

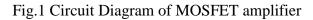

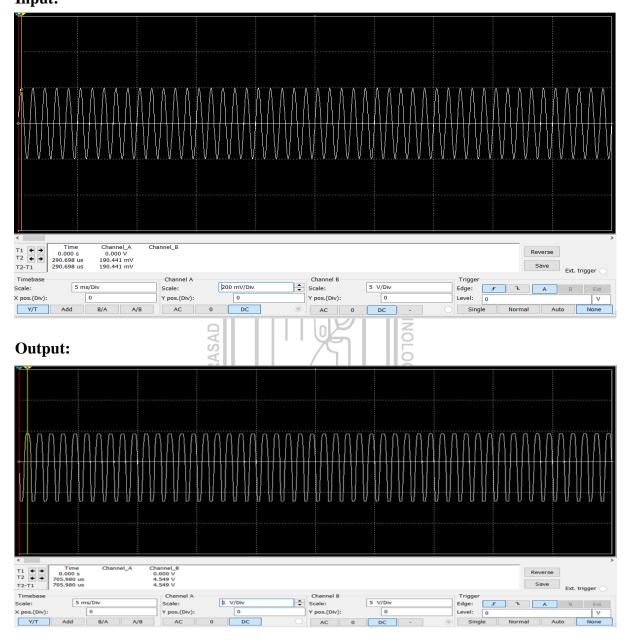

# Model Waveforms: Input:

# <u>Observations:</u> With Feedback

| Frequency(Hz)    | Output Voltage V <sub>0</sub> | $Gain = \frac{V_0}{V_i}$ | Gain in dB<br>$20\log(\frac{V_0}{V_i})$ |

|------------------|-------------------------------|--------------------------|-----------------------------------------|

|                  |                               |                          |                                         |

|                  |                               |                          |                                         |

| Without Feedback | SIDDHART                      | HA INS TITU              |                                         |

# Without Feedback

| Frequency(Hz) | Output Voltage Vo | $\operatorname{Gain}=\frac{V_0}{V_i}$ | TECHNOL | Gain in dB<br>$20\log(\frac{V_0}{V_i})$ |

|---------------|-------------------|---------------------------------------|---------|-----------------------------------------|

|               | ese<br>Vijay      | సి <sup>4</sup> భవ<br>WADA            | DGY     |                                         |

# **Precautions:**

- 1. Avoid loose connections

- 2. Don't switch on power supply while making connections

- 3. Handle components carefully

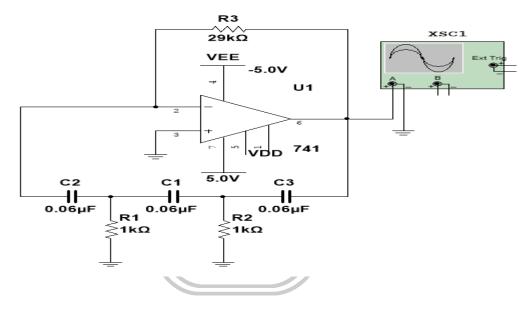

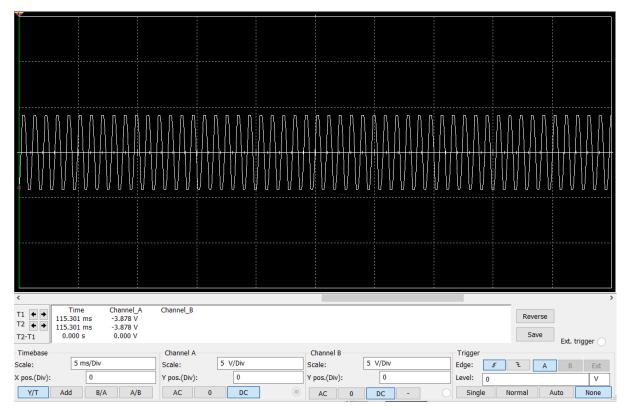

# **RC PHASE SHIFT OSCILLATOR**

<u>AIM:</u> To design an RC Phase Shift oscillator using op-amp for a given frequency

**Experimental Requirements**: Op-amp-741C Resistors Capacitors Fixed Power Supply -12V- 0-+12V CRO

#### **Circuit Diagram:**

#### **Design:**

The gain of feedback network is  $\beta = \frac{1}{29}$ .

To meet the greater than unity loop gain requirement, the closed loop voltage gain of op-amp must be greater than 29. That is  $-(\frac{R_F}{R_1}) \ge 29$

$R_F \ge 29 R_1$

Assume R<sub>1</sub>, find out R<sub>F</sub>

The frequency of output  $f_0 = \frac{1}{2\pi BC\sqrt{6}}$

For a given frequency, assume C, find out value of 'R'

### **Procedure:**

- 1. On a bread board set up the circuit as shown in the figure.

- 2. Obtain the sine wave in CRO.

- 3. Note down time period of sine wave & calculate its frequency

- 4. Compare theoretical and practical frequencies

#### Wave Forms:

#### **Precautions:**

- 1. Avoid loose connections

- 2. Do not switch on power supply while making connections

- 3. Handle components and apparatus carefully

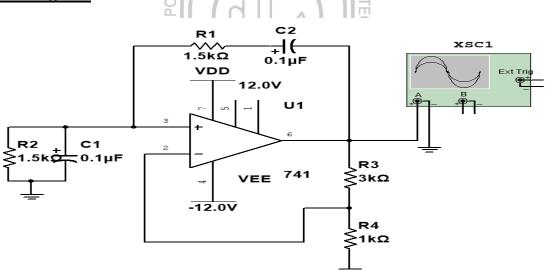

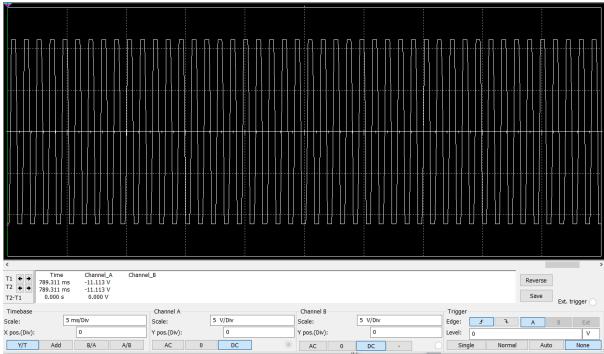

#### WEIN BRIDGE OSCILLATOR

#### AIM:

To design Wein Bridge oscillator using op-amp for a given frequency.

# **Experimental Requirements:**

1. Op-amp-741C

2.Resistors

3.Capacitors

4.Fixed Power Supply -12V- 0-+12V

5.CRO

#### Circuit Diagram:

#### **Design:**

The gain of feedback network is  $\beta = 1/3$ .

To meet the greater than unity loop gain requirement, the closed loop voltage gain of op-amp must be greater than 3. That is  $1+(R_F/R_1) >= 3$

$$R_F \ge 2 R_1$$

Assume R<sub>1</sub>, find out R<sub>F</sub>

The frequency of output  $f_0 = \frac{1}{2\pi RC}$  For a given frequency, assume C, find out value of 'R'

## Procedure:

1.On a bread board, set up the circuit as shown in the figure.

2.Obtain the sine wave in CRO

3.Note down time period of sine wave & calculate its frequency

4. Compare theoretical and practical frequencies

#### Wave forms:

#### **Precautions:**

- 1. Avoid loose connections

- 2. Do not switch on power supply while making connections

- 3. Handle components and apparatus carefully

# STUDY OF COLPITTS OSCILLATOR

# AIM:

To design and setup a colpitts oscillator using Op-amp and to observe the sinusoidal output waveform.

SIDDHARTHA INS TI

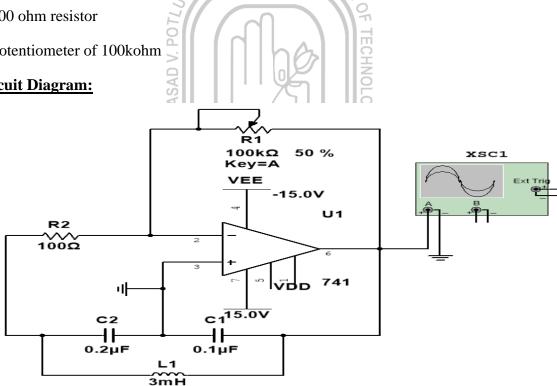

# **Experimental Requirements:**

- 1. Power- supply

- 2. Oscilloscope

- 3. Operational amplifier (µA741)

- 4. Decade capacitor

- 5. Decade inductor

- 6. 100 ohm resistor

- 7. Potentiometer of 100kohm

#### **Circuit Diagram:**

#### **Design Procedure:**

$$f_0 = \frac{1}{2\pi\sqrt{LC}}$$

Assume C, find out the value of L

# **Procedure:**

- 1. Connect the circuit shown in Fig, with L=3mH, Cl=C2=2 $\mu$ F. Draw the output & measure (f<sub>o</sub>).

- 2. For C1=C2=2 $\mu$ f, vary (L) from (3 to 9)mH. Then measure output frequency in each case.

- 3. For L=3mH, C2=2 $\mu$ F, vary Cl from (2 $\mu$ F to 8 $\mu$ F). Then measure output frequency in each case.

- 4. For L=3mH, C1=2 $\mu$ F, vary C2 from (2uF to 8 $\mu$ F). Then measure output frequency in each case.

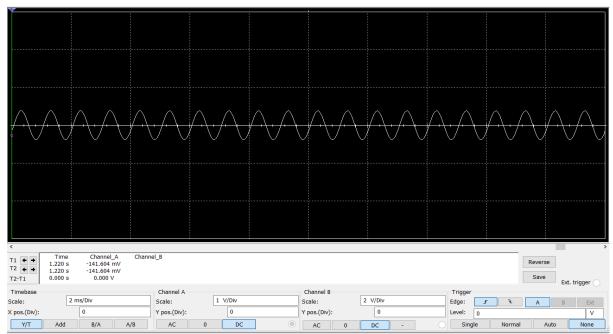

# Waveform:

| Y IIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                |                                             |          |                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------|----------|------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                |                                             |          |                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                |                                             |          |                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                |                                             |          |                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                |                                             |          |                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                |                                             |          |                              |

| Channel_A Channel_A Channel_A Channel_A Channel_A Channel_A Channel Channel Channel_A Channel Channel_A Channel Channel_A Channel Channel_A Channel Channel_A Channel Channel_A Channel Channel Channel_A Chane Channel_A Channel_A Channel_A | el_B                                           |                                             |          | Reverse<br>Save Ext. trigger |

| Timebase       Scale:     500 us/Div       X pos.(Div):     0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Channel A<br>Scale: 10 V/Div<br>Y pos.(Div): 0 | Channel B<br>Scale: 5 V/D<br>Y pos.(Div): 0 | Level: 0 | A B Ext                      |

| Y/T Add B/A A/B<br>Precautions:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | AC 0 DC                                        | VIJATAVVAJA                                 | - Single | Normal Auto None             |

- 1. Avoid loose connections

- 2. Do not switch on power supply while making connections

- 3. Handle components and apparatus carefully

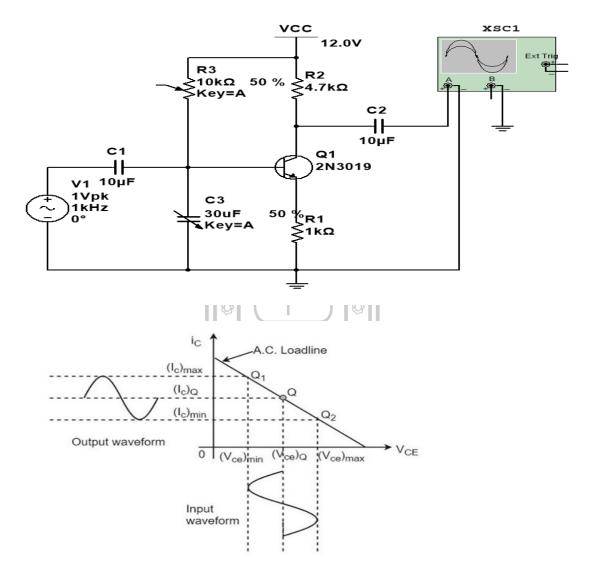

#### **CLASS A POWER AMPLIFIER USING BJT**

# AIM:

To construct and find the Gain of the class A power amplifier using BJT.

Experimental Requirements: PC loaded with Multisim

#### **Circuit Diagram:**

**Design:**

$$\eta = \frac{output \ power}{input \ power} \times 100 = \frac{P_{out}}{P_{in}} \times 100$$

$$\eta = \frac{P_{ac}}{P_{dc}} \times 100$$

17

$$\eta = \frac{V_m I_m}{2V_{CC} I_C} \times 100$$

We know that

$$V_m = \frac{V_{max} - V_{min}}{2} \cong V_{CEQ} \cong \frac{V_{cc}}{2}$$

$I_m \cong I_C$

#### **Procedure:**

1. Open the Multisim software in the system.

2. Build the circuit as shown in the diagram.

3. Calculate the efficiency of the Class A power amplifier.

#### Waveform:

### **Precautions:**

Design the circuit without any disconnections

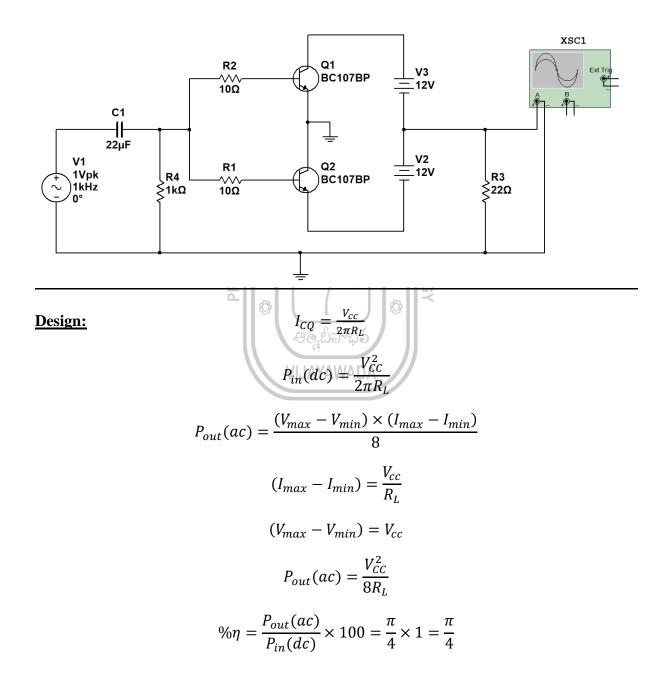

#### **CLASS B COMPLIMENTARY SYMMETRY AMPLIFIER**

### AIM:

To find the efficiency of a complimentary symmetry class B power amplifier.

Experimental Requirements: PC loaded with Multisim.

#### **Circuit Diagram:**

# **Procedure:**

- 1. Open the Multisim software in the system.

- 2. Build the circuit as shown in the diagram.

- 3. Calculate the efficiency of the Class A power amplifier.

#### Waveform:

# **RC DIFFERENTIATOR USING OP AMP**

#### AIM:

To Design and Simulate the RC differentiator using Op-Amp

Experimental Requirements: PC loaded with multisim software

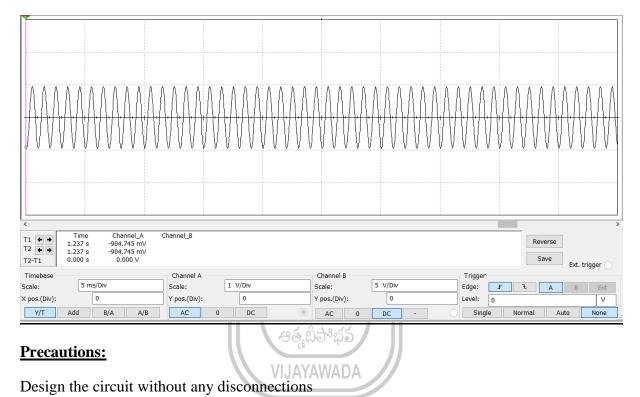

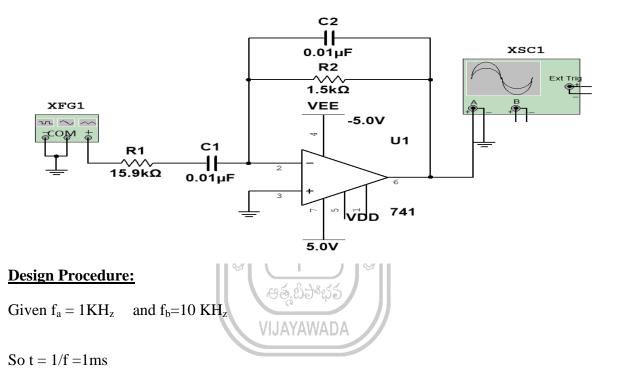

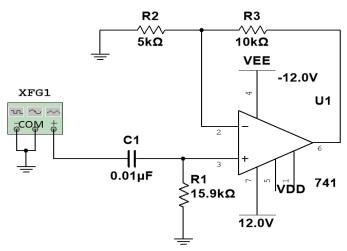

#### **<u>Circuit Diagram:</u>**

Design equation  $T=1/2\pi R_1C_1$ Let  $C_1=0.01 \ \mu F$  then  $R_1=15.9k\Omega$

For  $f_a = 10 f_b$

Take  $R_f=10R_i=1.5k\Omega$  and  $C_f=0.01 \ \mu F$

# Procedure:

- 1. Switch on pc

- 2. Open multisim software

- 3. Setup the circuit on and check the connections.

- 4. Give  $Vi=2V_{pp}$ , 1KHz square wave.

- 5. Keep the oscilloscope in AC coupling mode.

- 6. Observe input and output on two channels of the oscilloscope simultaneously.

- 7. Draw the input and output waveforms on the graph

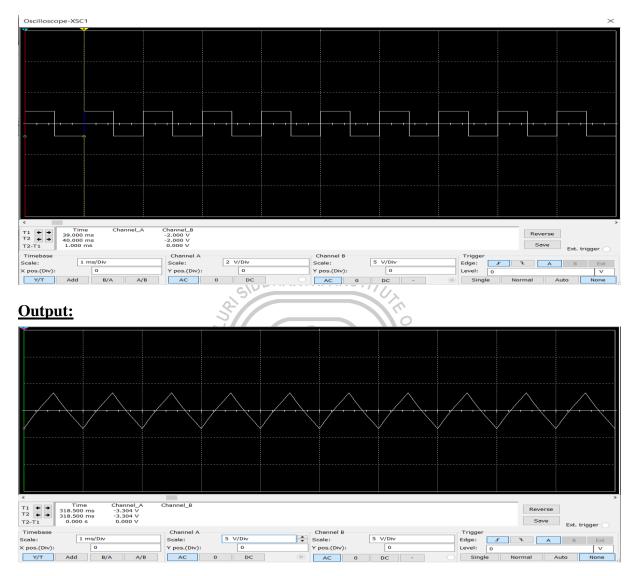

# Waveforms:

# Input:

# **Precautions:**

- 1. Check your connections before observing graph

- 2. Handle your pc carefully

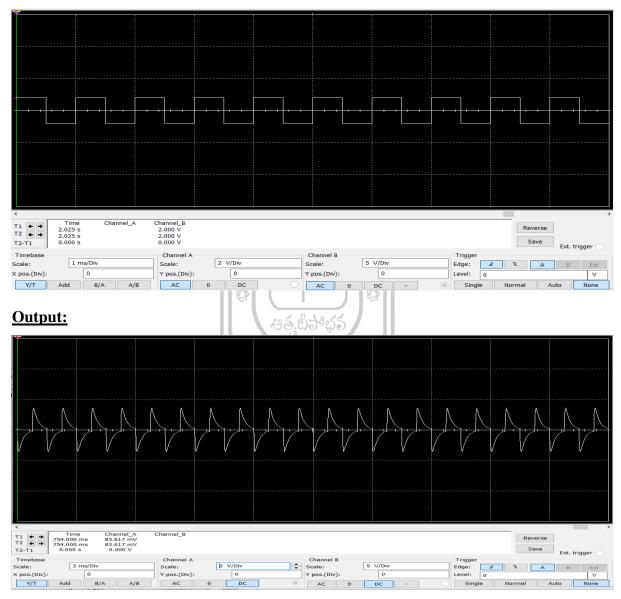

## **RC INTEGRATOR USING OP-AMP**

# <u>AIM</u>:

To design and setup an integrator circuit using op amp IC741 and plot its response

Experimental Requirements: PC loaded with multisim software

### **Circuit Diagram:**

Let C=0.01  $\mu$ F then R<sub>i</sub>=15K $\Omega$

Take  $R_f=10R_i=150K\Omega$

#### **Procedure:**

- 1. Switch on pc

- 2. Open multisim software

- 3. Setup the circuit on and check the connections.

- 4. Give Vi= 2Vpp, 1KHz square wave.

- 5. Keep the oscilloscope in AC coupling mode.

- 6. Observe input and output on two channels of the oscilloscope simultaneously.

- 7. Draw the input and output waveforms on the graph

# Wave forms:

# Input:

# **Precautions:**

- 1. Check your connections before observing graph

- 2. Handle your pc carefully

### ADDER AND SUBTRACTOR CIRCUITS USING OP-AMP

## AIM:

To design and verify the adder and subtractor circuits using Op-amp circuits.

## **Experimental Requirements:**

- 1. IC 741

- 2. 4 Resistor  $(1K\Omega)$

- 3. Regulated power supply

- 4. IC breadboard trainer

- 5. Patch cords

- 6. Multimeter

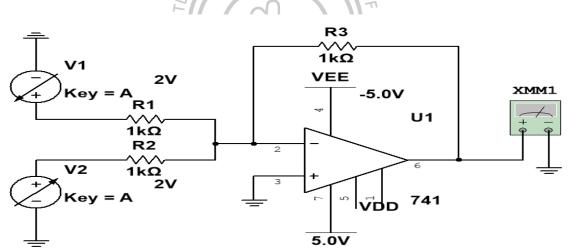

## **Circuit Diagram:**

#### Adder:

SID DHARTHA INS 7

#### Subtractor:

#### **Design Procedure:**

### Adder circuit:

$V_o = -(V_1 + V_2)$

If  $V_1 = 2V$  and  $V_2 = 2V$ , then

$V_0 = -(2+2) = -4V.$

#### Subtractor circuit:

$V_{o} = V_{2} - V_{1}$

If  $V_1=4$  and  $V_2=2$ , then

$V_o = 4 - 2 = -2$

#### Procedure:

#### Adder circuit:

- 1. Connect the circuit as per the diagram.

- 2. Apply the supply voltages of +15V to pin7 and pin4 of IC741 respectively.

- 3. Apply the inputs  $V_1$  and  $V_2$  as shown.

- 4. Apply two different signals (DC/AC) to the inputs.

- 5. Vary the input voltages and note down the corresponding output at pin 6 of the IC 741 adder circuit.

- 6. Notice that the output is equal to the sum of the two inputs.

#### Subtractor circuit:

- 1. Connect the circuit as per the diagram.

- 2. Apply the supply voltages of +15V to pin7 and pin4 of IC741 respectively.

- 3 Apply the inputs  $V_1$  and  $V_2$ .

- 4. Apply two different signals (DC/AC) to the inputs.

- 5. Vary the input voltages and note down the corresponding output at pin 6 of the IC 741 subtractor circuit.

- 6. Notice that the output is equal to the difference of the two inputs.

# **Output:**

#### Adder:

#### **Subtractor:**

# Adder circuit:

| V <sub>1</sub> | V <sub>2</sub> | V <sub>o/p</sub> |

|----------------|----------------|------------------|

|                |                |                  |

|                |                |                  |

# **Subtractor Circuit:**

| V <sub>1</sub> | $V_2$           | V <sub>O/P</sub> |

|----------------|-----------------|------------------|

|                |                 |                  |

|                |                 |                  |

|                | DHARTHA INS T/> |                  |

# **Precautions:**

- 1. Make null adjustment before applying the input signal

- 2. Maintain proper  $V_{CC}\,$  levels

- 3. Don't switch ON power supply while making connections.

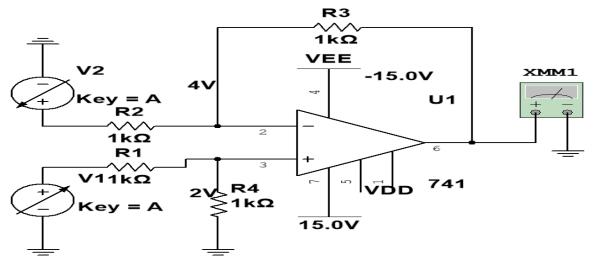

#### **ASTABLE MULTIVIBRATOR USING 555 TIMER**

# AIM:

To Design and verify an Astable multivibrator using 555 timer

. POTLUR,

#### **Experimental Requirements:**

- 1. <u>IC 555 Timer</u>

- 2. Resistors (10 K $\Omega$ , 4.7 K $\Omega$ )

- 3. Diode (IN 4007)

- 4. Capacitors (0.1µF, 0.01µF)

- 5. CRO

- 6. Patch cards

- 7. CRO Probes

- 8. Connecting wires

#### **Circuit Diagram:**

SIDDHARTHA INS TI

#### **Design:**

Theoretically without diode charging time Tc is given by Tc= $0.69(R_1+R_2)$  C1,

Discharging time Td is given by  $Td = 0.69R_2C_1$

The frequency f is given by  $f = 1.45/(R_1+2R_2)C_1$

% of Duty cycle is  $(T_c / (T_c + T_d))*100$

#### Procedure:

- 1. Connections are made as per the circuit diagram.

- 2. Pins 4 and 8 are shorted and connected to power supply Vcc (+5V)

- 3. Between pins 8 and 7 resistor  $R_1$  of  $10K\Omega$  is connected and between 7 and 6 resistor R2 of  $4.7K\Omega$  is connected. Pins 2 and 6 short circuited.

- 4. In between pins 1 and 5 a Capacitor of  $0.01 \mu$ F is connected.

- 5. The output is connected across the pin 3 and GND.

- 6. In between pins 6 and GND a Capacitor of  $0.1\mu$ F is connected.

- 7. Theoretically without diode charging time Tc is given by  $T_c=0.69(R_1+R_2) C_1$ , Discharging time  $T_d$  is given by  $T_d=0.69R_2C_1$

The frequency f is given by  $f = 1.45/(R_1+2R_2)C_1$

% of Duty cycle is  $(T_c / (T_c + T_d))*100$  THA INS 7/7

- 8. Practically T<sub>d</sub> and T<sub>c</sub> are measured and wave forms are noted and theoretical Values are verified with practical values

- 9. Connect diode between pins 7 and 2.

- 10. Theoretically with diode connected charging time is given by Tc=0.69R<sub>1</sub>C<sub>1</sub> Discharging time is given by

VIJAYAWADA

$Td=0.69R_2C_1$

11.Practically  $T_d$  and  $T_c$  are noted and verified with theoretical values.

#### Wave Forms:

| Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                     |         |                                                                                   |                                            |                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------|-----------------------------------------------------------------------------------|--------------------------------------------|------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                     | $\sim$  |                                                                                   |                                            | ~~~~                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                     |         |                                                                                   |                                            |                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                     |         |                                                                                   |                                            |                                    |

| < T1  Time T1 T2 T2 T2 T1 T2 | Channel_A Channel_<br>2.299 V<br>2.299 V<br>0.000 V |         |                                                                                   |                                            | Reverse Save Ext. trigger          |

| Timebase       Scale:     2 ms/Div       X pos.(Div):     0       Y/T     Add     B/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Channel A<br>Scale:<br>Y pos.(Div)<br>A/B AC        | 5 V/Div | Channel B       Scale:     5 V/Div       Y pos.(Div):     0       AC     0     DC | Trigger<br>Edge: F<br>Level: 0<br>Single 1 | L A B Ext   V V   Normal Auto None |

# **Precautions:**

1. Make null adjustment before applying the input signal

2.Maintain proper Vcc levels OHARTHA INS זי 3.Handle components care fully Result:

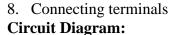

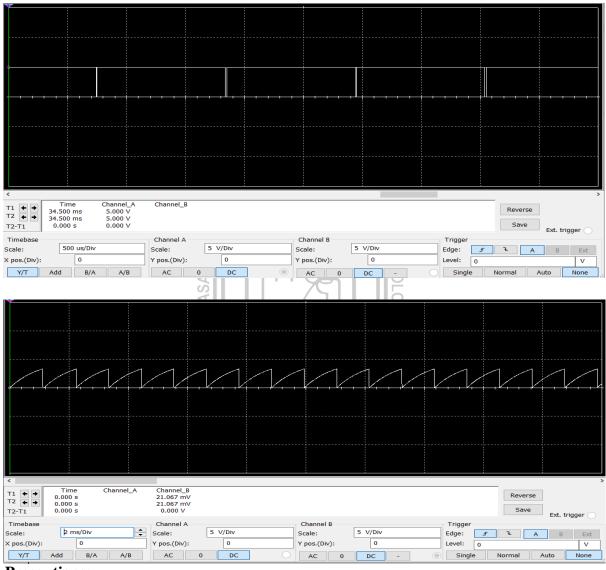

#### MONOSTABLE MULTIVIBRATOR USING 741 OP- AMP

### AIM:

To construct a monostable multivibrator using operational amplifier 741 and to determine the duration of the output pulse generated and to compare it with that of theoretical value.

SIDDHARTHA INS TIT

#### **Experimental Requirements:**

- 1. Operational amplifier(IC741)

- 2. CRO

- 3. RPS

- 4. 4 Non inductive fixed resistors (R<sub>1</sub>, R<sub>2</sub>, R<sub>4</sub> and R<sub>5</sub>)

- 5. 1 Non inductive Variable resistor (R<sub>3</sub>)

- 6. 2 Capacitors( $C_1$  and  $C_2$ )

- 7. 3 Diodes( $D_1$ ,  $D_2$  and  $D_3$ )

#### **Design Procedure:**

$$V_C = -V_{out} + (V_{out} + V_D)e^{-t/\tau}$$

At instant,  $t = \tau$  and  $V_c = -\beta V_{out}$ , where  $\beta = \frac{R_2}{R_1 + R_2} = Feedback Factor$

So,

$$-\beta V_{out} = -V_{out} + (V_{out} + V_D)e^{-t/\tau}$$

31

where Time Constant,  $\tau = R_3 C_1$

$$V_{out}(1-\beta) = V_{out} \left(1 + \frac{V_D}{V_{out}}\right) e^{-T/\tau}$$

In general,  $V_D \ll V_{out}$

so  $(1-\beta) = e^{-T/\tau}$

$$T = R_3 C_1 \log_e \frac{1}{1 - \beta}$$

$T = 0.69R_3C_1$

Substuition of  $\beta = \frac{R_2}{R_1 + R_2}$ , assume  $R_1 = R_2$  gives  $\beta = \frac{1}{2}$ . Upon substitution of these values in above equation, gives

#### **Procedure:**

1. Connect the circuit as shown in the figure.

2. Take the  $R_1=R_2=1K\Omega$ ,  $C_1=C_2=0.1\mu F$  and  $R_3=10K\Omega$  (variable resistance) or any convenient values.

3. Apply the DC power supplies to the terminals (7) and (4) of the operational amplifier.

4. Keep the R<sub>3</sub> value at a convenient value AYAWADA

5. Set the voltage sensitivity band switch of the Y- plate and time base band switch of C.R.O. to the convenient positions such that at least two or more complete square wave forms are observed on the screen of CRO. The length of –ve value or  $-V_{out}$  is the duration of the quasi-stable state.

6. Now measure the horizontal length (l) of the quasi-stable state. Also note the time base value (m) of the X-plates of the CRO in the table.

7. From this calculate the time duration of the quasi- stable state. This is the experimental value. Similarly the theoretical value can also be calculated by substituting the values of  $R_3$ ,  $R_1$ ,  $R_2$  and  $C_1$  in the above given equation.

8. Now the experiment is repeated for different values of  $R_3$  by increasing its value in equal steps (Multiples of 100  $\Omega$ ).

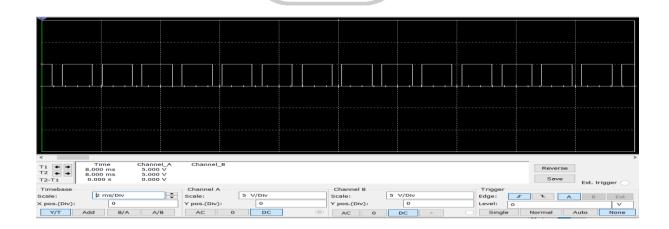

#### Wave Forms:

#### **Precautions:**

- 1. Make sure there are no circuit breaks

- 2. Take the values without any error.

#### MONOSTABLE MULTIVIBRATOR USING 555 TIMER

#### AIM:

To design and verify the operation of a monostable multivibrator using 555 timer.

**Experimental Requirements:**

- 1. 555 IC Timer

- 2. Capacitors( $0.1\mu$ F,  $0.01\mu$ F)

- 3. Resistors( $10k\Omega$ )

- 4. Bread board IC Trainer

- 5. CRO

- 6. Connecting wires and patch cords

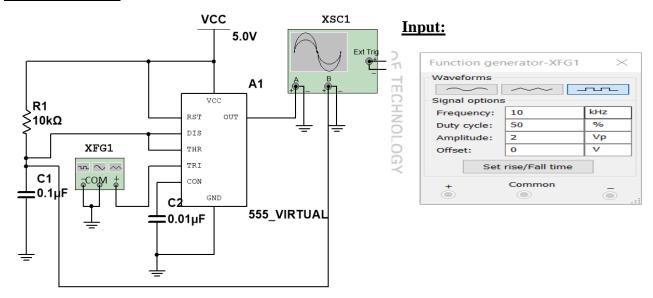

#### **Circuit diagram:**

#### **Design:**

$$V_o = V_f + (V_i - V_f)e^{t/R}$$

$$\beta = \frac{R_2}{R_1 + R_2}$$

if  $V_{sat} \gg V_p$  and  $R_1 = R_2$ ,  $\beta = 0.5$

Then T = 0.69RC

#### **Procedure:**

1. Connect the circuit as shown in the circuit diagram.

2. Apply Negative triggering pulses at pin 2 of frequency 1 KHz as shown in Fig.

3. Observe the output waveform and capacitor voltage as shown in Figure and measure the pulse duration.

4. Theoretically calculate the pulse duration as Thigh =1.1 RC 5. Compare it with experimental values.

Wave forms:

- **Precautions:**

- 1. Make sure there are no circuit breaks

- 2. Take the values without any error.

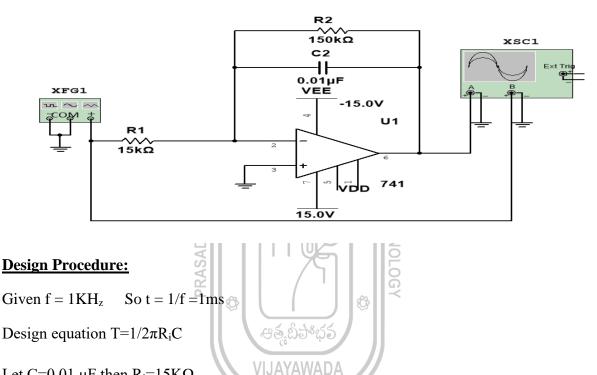

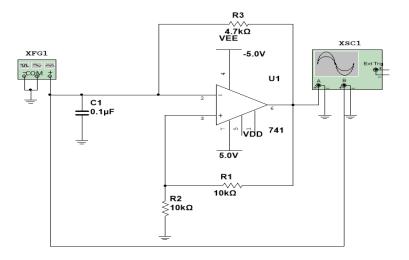

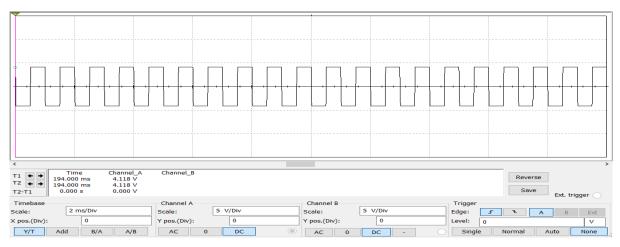

#### ASTABLE MULTIVIBRATORS USING IC 741 OP AMP

### AIM:

To design and verify symmetrical and asymmetrical Astable multivibrators using Op- amp 741 ,plot the waveforms and measure the frequency of oscillation

SIDDHARTHA INS T

#### **Experimental Requirements:**

Dual power supply +/- 15V -1

Function generator (0- 1MHz) -1

Oscilloscope-1

Bread Board -1

IC741 -1

**Resistors-5**

Capcaitors-0.1µF -2

Diode 1N4007-2

Probes and connecting wires- as required 5.85%

# SYMMETRCAL ASTABLE MULTIVIBRATOR:

POTL

PRASAD V.

Ô

#### Circuit Diagram:

Input:

ECHNOLOGY

Ô

| Function generator-XFG1 $\qquad$ $	imes$ |          |      |  |  |  |  |  |

|------------------------------------------|----------|------|--|--|--|--|--|

| Waveforms                                |          |      |  |  |  |  |  |

| $\sim$                                   | <u> </u> |      |  |  |  |  |  |

| Signal options                           |          |      |  |  |  |  |  |

| Frequency:                               | 1        | kHz  |  |  |  |  |  |

| Duty cycle:                              | 50       | %    |  |  |  |  |  |

| Amplitude:                               | 4        | Vp   |  |  |  |  |  |

| Offset:                                  | 0        | V    |  |  |  |  |  |

| Set rise/Fall time                       |          |      |  |  |  |  |  |

| +                                        | Common   | ē .: |  |  |  |  |  |

#### **Design:**

Given f = 1 KHz

So,  $T = \frac{1}{f} = 1msec$

And

$$\beta = \frac{R_2}{R_1 + R_2}$$

Let  $R_1 = 10 \text{ k}\Omega$ , and  $R_2 = 10 \text{ k}\Omega$

Then  $\beta = 0.5$

Therefore, T = 2.2RC = 1msec

Let  $C = 0.1 \mu F$ , then  $R = 4.7 k \Omega$

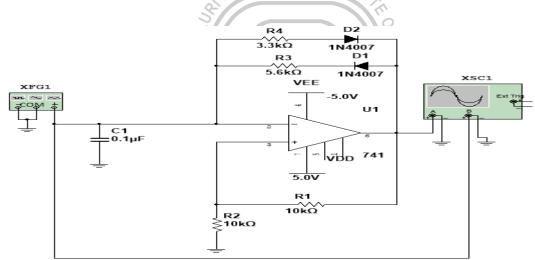

# ASYMMETRCAL ASTABLE MULTIVIBRATOR:

#### **Design:**

Given f = 1 KHz

So

$$T = T_{ON} + T_{OFF} = \frac{1}{f} = 1msec$$

Also Duty Cycle =  $\frac{T_{ON}}{T_{ON}+T_{OFF}} = 0.66$  or 66%.

Solving above two equations,  $T_{ON} = 0.66msec$ ,  $T_{OFF} = 0.33msec$

For  $\beta$ =0.5, ,  $T_{ON} = 1.1 R_{f1} C = 0.66 msec$

37

Let  $C = 0.1 \mu F$

Then  $R_{fl}$  = 6.2k $\Omega$  , use 5.6K $\Omega$  (Std)

$T_{OFF} = 1.1 R_{f2} C = 0.33 msec$

Similarly,  $T_{off} = 1.1R_{f2}C = 0.33ms$

Then  $R_{f2} = 3k\Omega$ , use 3.3 K $\Omega$  (Std)

#### **Procedure:**

- 1. Connect the circuit as shown in the circuit diagram.

- 2. Observe the output waveform and capacitor voltage as shown in Figure and measure the

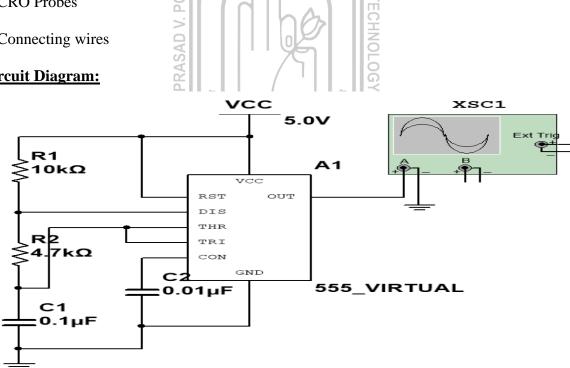

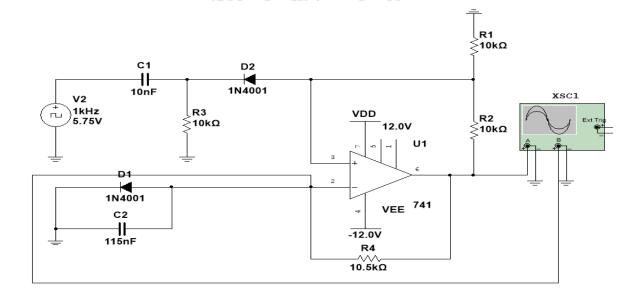

# Wave Forms:

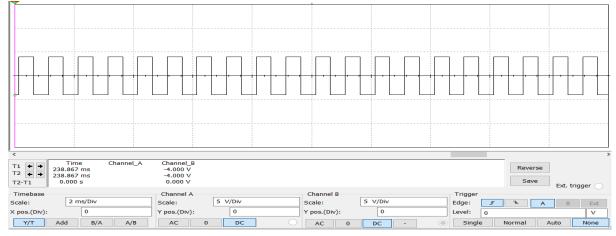

# SYMMETRICAL WAVE FORM

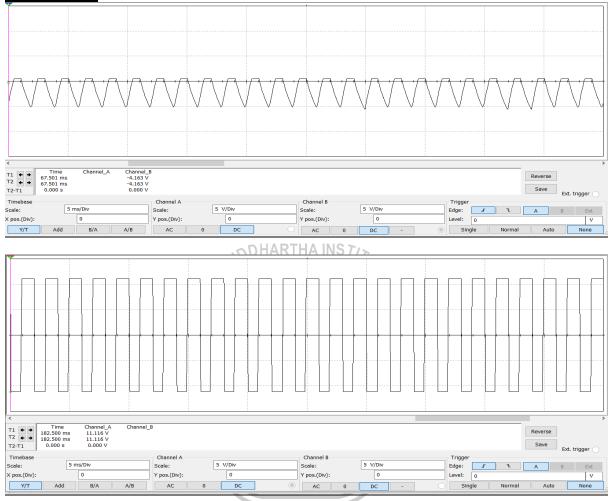

# **ASYMMETRICAL WAVEFORM:**

| <                                         | · · · ·                     |                             | >                            |  |  |

|-------------------------------------------|-----------------------------|-----------------------------|------------------------------|--|--|

| T1 + Time Channel_A<br>79.413 ms -4.116 V | Channel_B                   |                             | Reverse                      |  |  |

| T2 + > 79.413 ms -4.116 V                 |                             |                             |                              |  |  |

| T2-T1 0.000 s 0.000 V                     |                             |                             | Save Ext. trigger            |  |  |

| Timebase<br>Scale: 2 ms/Div               | Channel A<br>Scale: 5 V/Div | Channel B<br>Scale: 5 V/Div | Trigger<br>Edge: F & A B Ext |  |  |

| X pos.(Div): 0                            | Y pos.(Div): 0              | Y pos.(Div): 0              | Level: 0 V                   |  |  |

| Y/T Add B/A A/B                           | AC 0 DC O                   | AC 0 DC -                   | Single Normal Auto None .    |  |  |

|                                           |                             |                             |                              |  |  |

|                                           |                             |                             |                              |  |  |

| VIJATAWADA                                |                             |                             |                              |  |  |

|                                           |                             |                             |                              |  |  |

# **Precautions:**

- 1. Make sure there are no circuit breaks

- 2. Take the values without any error.

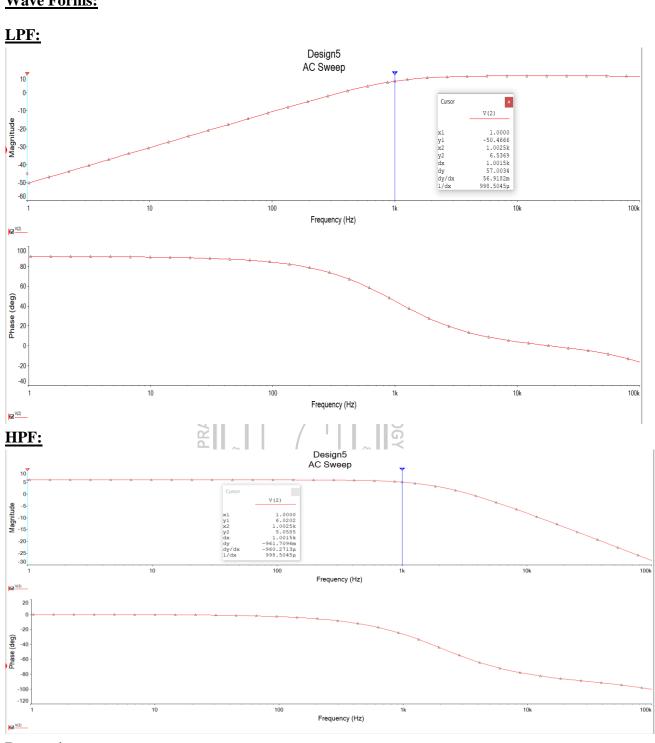

#### LPF AND HPF USING OP-AMP

# AIM:

To design and the Lowpass and Highpass filters using Op-amp.

#### **Experimental Requirements:**

- 1. Signal Generator

- 2. Op-amp(IC741)

- 3. Resistors(1k,1.5k,5k,10k)

- 4. Capacitor $(0.1 \mu f)$

- 5. Linear power supply

- 6. Digital storage oscilloscope(DSO)

#### **Circuit Diagram:**

HPF:

40

Design :

$$f_c = \frac{1}{2\pi RC} = \frac{1}{2\pi \tau}$$

, where  $\tau = RC$

$Gain = \left(1 + \frac{R_f}{R_i}\right)$

# **Procedure:**

1. Connect the circuit as shown in the diagram.

2.Connect the DSO to the probes and switch it on.

<u>3.</u>Check the graph for both positive and negative voltage and note down the output.

# Tabular Forms:

# Lowpass Filter:

| Input Output Gain   Frequency (Hz) Voltage (V) |            | HAINSTIT | DHART       |                  |

|------------------------------------------------|------------|----------|-------------|------------------|

| Od 'A GASAR                                    | Gain in dB | Gain     | Output      | Input            |

| DOTOR ASAD                                     |            |          | Voltage (V) | Frequency (Hz)   |

| SVAd B Cry B LOCY                              |            |          | AD V. H     |                  |

| తి ఆత్యబిపిశిభవ                                |            |          | PRAS        |                  |

|                                                |            | 19455 B  |             |                  |

| Highpass Filter: VIJAYAWADA                    |            |          | VIIAV       | Highnass Filter. |

| Г_              |              |      |            |

|-----------------|--------------|------|------------|

| Input           | Output       | Gain | Gain in dB |

|                 |              |      |            |

| Frequency (Hz)  | Voltage (V)  |      |            |

| riequency (IIZ) | () on age () |      |            |

|                 |              |      |            |

|                 |              |      |            |

|                 |              |      |            |

|                 |              |      |            |

|                 |              |      |            |

|                 |              |      |            |

|                 |              |      |            |

|                 |              |      |            |

|                 |              |      |            |

|                 |              |      |            |

|                 |              |      |            |

|                 |              |      |            |

41

#### **Wave Forms:**

**Precautions:**

1.Make sure that there are no loose connections 2.Power off the supply while making the connections **<u>Result:</u>**

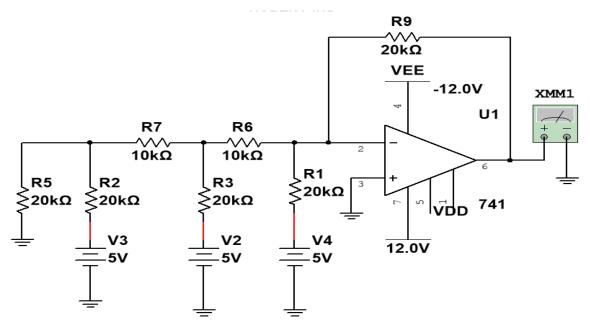

#### **4-BIT DAC USING OP-AMP**

#### AIM:

To construct and to study the Digital to analog convertor circuit using Op-amp.

#### **Experimental Requirements:**

- 1. IC741

- 2. Multimeters patch

- 3. Connecting cards

- 4. Resistors (1k,2k,8k)

- 5. IC breadboard trainer

#### **Circuit diagram:**

#### **Procedure:**

- 1. Connections are made as per circuit diagram.

- 2. Pin2 is connected to resistor  $1M\Omega$  and ground.

- 3.  $+V_{cc}$  are available at Pin7 and  $-V_{cc}$  is applied atPin4.

- 4. Output is taken between pin6 and ground

- 5. Voltage at each bit (vr) is found at bits b0, b1, b2, b3.

- 6. Pin3 of op amp is connected to resistor  $1k\Omega$  and is given to b3 (msb).

- 7. A resistor of  $2k\Omega$  is connected between pin2 and pin 6 of op amp

# **Tabular forms:**

| D3 | D2 | D1 | D0 R-2R Lade |             | DAC(V)    |

|----|----|----|--------------|-------------|-----------|

|    |    |    |              | Theoretical | Practical |

|    |    |    |              |             |           |

|    |    |    |              |             |           |

|    |    |    |              |             |           |

|    |    |    |              |             |           |

|    |    |    |              |             |           |

|    |    |    |              |             |           |

|    |    |    |              |             |           |

# **Precautions:**

# Result:

SIDDHARTHA INS TIT